# Matrox Helios eCL/XCL >>

High-speed Camera Link® frame grabber with powerful pre-processing capabilities.

#### Key features

- > x4 PCle™ (eCL) or PCI-X® (XCL) card

- handles two fully independent Base or a single Full Camera Link® configuration(s)1

- acquires up to 680 MB per second

- > up to 512 MB of DDR SDRAM memory

- > performs complete image reconstruction from multi-tap frame and line-scan cameras

- over 5 GB per second of memory bandwidth

- > powerful pre-processing core capable of up to 100 BOPS<sup>2</sup>

- ➤ up to 1 GB per second of I/O bandwidth to host PC

- > serial communication ports can be mapped as PC COM ports

- > support for rotary encoders with quadrature output

- programmed using Matrox Imaging Library (MIL) sold separately

- > supports 32/64-bit Microsoft® Windows® XP/ Vista®/7 and 32/64-bit Linux®

- > royalty-free redistribution of MIL's image processing module

#### Exceptional video capture rates and more

Matrox Helios eCL/XCL is the new standard in high-performance Camera Link® frame grabbers. It fully exploits PCIe<sup>TM</sup>/PCI-X<sup>®</sup> technology to deliver unprecedented video capture rates for a single-board solution and can easily accommodate the most demanding Camera Link® cameras. A custom ASIC, designed by Matrox, integrates a powerful processor core to alleviate the host CPU from image formatting and pre-processing tasks. These features provide the Matrox Helios eCL/XCL with the power and flexibility needed for vision applications of today and tomorrow.

# Complete Camera Link® frame grabber

The Matrox Helios eCL/XCL is available in one of two factory-configured versions. The dual-Base version enables simultaneous acquisition from two completely independent Camera Link® cameras utilizing the Base configuration1. The single-Full configuration acquires from a single Camera Link® camera utilizing the Base, Medium or Full configuration<sup>1</sup>. Both versions can handle the most popular frame and line scan cameras including the complete image reconstruction from outputs using multiple taps, and can operate at full Camera Link® speed. The Matrox Helios eCL/XCL also includes an internal video generator for troubleshooting installation and operation.

#### Choice of high-performance host bus interfaces

Four lane (x4) PCIe™ and PCI-X® are the interfaces used to connect to the host PC on the Matrox Helios eCL and Matrox Helios XCL boards respectively. PCIe™ is the follow-on to conventional PCI and PCI-X®. Version 1.x of PCIe<sup>™</sup> operates at 2.5 GHz to deliver a peak bandwidth of 1GB/sec over a x4 implementation. PCI-X® is a high-performance backwards-compatible enhancement to conventional PCI. Version 1.0a of PCI-X® specifies a 64-bit physical connection running at speeds of up to 133 MHz resulting in a peak bandwidth of up to 1 GB per second.

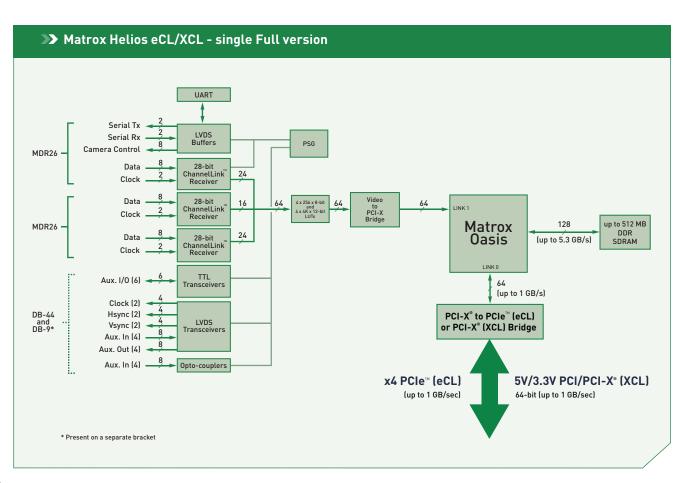

#### >> Matrox Helios eCL/XCL - dual Base version UART Serial Tx -LVDS Buffers Serial Rx PSG #1 Camera Control MDR26 8 Data 28-bit ChannelLink Receiver 2 x 256 x 8-bit Clock 2 x 4K x 12-bit LUTs UART 2,4 up to 512 MB 128 **Matrox** 2 x 4K x 12-bit LUTs DDR SDRAM **Oasis** (up to 5.3 GB/s) Serial Tx LVDS Serial Rx Buffers PSG #2 Camera Control MDR26 64 28-bit ChannelLink Receiver Data (up to 1 GB/s) PCI-X® to PCIe™ (eCL) or PCI-X® (XCL) Bridge TTL Transceivers Aux. I/O (6) Clock (2) DB-44 and DB-9\* Hsync (2) 🔫 LVDS Transceivers Vsync (2) 🔫 x4 PCle™ (eCL) 5V/3.3V PCI/PCI-X° (XCL) Aux. In (4) (up to 1 GB/sec) 64-bit (up to 1 GB/sec) Aux. Out (4) Aux. In (4) -Opto-couplers \* Present on a separate bracket

#### State-of-the-art Matrox Oasis ASIC

The Matrox Imaging designed Oasis ASIC is the pivotal component of the Matrox Helios eCL/XCL. A high-density chip, the Matrox Oasis integrates a Links Controller, main memory controller and Pixel Accelerator.

#### **Pixel Accelerator**

The Pixel Accelerator (PA) is a parallel processor core, which considerably accelerates neighborhood, point-to-point and LUT mapping operations. It consists of an array of 64 processing elements all working in parallel. Each processing element has a multiply-accumulate (MAC) unit and an arithmetic-logic unit (ALU).

The MAC unit is capable of performing a single 16-bit by 16-bit, two 8-bit by 16-bit or four 8-bit by 8-bit multiplies with 40-bit accumulation per cycle for convolution operations. The 40-bit accumulator guarantees no overflow situation for a 16 by 16 kernel with 16-bit coefficients and data. In addition, the PA architecture allows symmetrical kernels to be processed four times faster. The MAC unit can perform up to four minimum or maximum operations per cycle for grayscale morphology operations.

The ALU can execute a wide variety of arithmetic and logical operations. It can be programmed to execute a sequence of 256 instructions per pixel at one instruction per cycle reducing the amount of memory accesses and further accelerating memory I/O-bound sequences. The PA can accept up to four source buffers³ and output to four destination buffers allowing several operations to be performed at once or in a single pass (e.g., four images can be averaged in one pass). Operating at a core frequency of 167 MHz enables the PA to carry out up to 100 BOPS² (i.e., process over two billion pixels per second).

#### Memory controller

The Matrox Oasis includes a very efficient main memory controller for managing the 128-bit wide interface to DDR SDRAM memory. Operating at 167 MHz, the DDR SDRAM memory and controller combine to deliver a memory bandwidth in excess of 5 GB

per second. Such ample memory bandwidth allows the Matrox Helios eCL/XCL to comfortably handle demanding video I/O while maintaining PA performance even for memory I/O-bound operations.

### **Links Controller**

The Links Controller (LINX) is the router that manages all data movement within the Matrox Helios eCL/XCL. It oversees the transfer of image data from the frame grabber section to onboard memory for pre-processing and from onboard memory to the host PC including display. Image data can be subject to various formatting operations including plane separation on input and merging on output, input cropping, input and output sub-sampling (1 to 16), and independent control of horizontal and vertical scanning direction. The latter is particularly useful for reconstructing a proper image from a camera whose readout requires multiple taps, each with different scanning directions.

#### Field-proven application development software

Matrox Helios eCL/XCL is supported by the Matrox Imaging Library (MIL), a comprehensive collection of software tools for developing industrial imaging applications. MIL features interactive software and programming functions for image capture, processing, analysis, annotation, display and archiving. These tools are designed to enhance productivity, thereby reducing the time and effort required to bring your solution to market. Refer to the MIL datasheet for more information

MIL's image processing module, when used with the Matrox Helios eCL/XCL, comes with royalty-free redistribution rights. The image processing module, which includes functions for basic arithmetic, logic, LUT mapping, per pixel gain and offset, morphology, spatial filtering, statistics, temporal filtering and threshold, is fully optimized for the PA4. Support for custom PA functions is also available on demand and upon evaluation.

#### **Specifications**

#### Hardware

- x4 PCIe<sup>™</sup> card or PCI/PCI-X<sup>®</sup>card with universal 64-bit card edge connector (64-bit 33/66 MHz 5/3.3V PCI and 64-bit 66/100/133 MHz PCI-X)

- up to 512 MB of 167 MHz DDR SDRAM main memory

- · two factory configured versions

- two independent Camera Link® Base ports¹ (dual-Base)

- single Camera Link® Base/Medium/Full port¹ (single-Full)

- Channel Link speed of up to 85 MHz

- supports frame and line-scan video sources

- full reconstruction from multi-tap sources

- four 256 x 8-bit and four 4K x 12-bit LUTs

- six TTL configurable auxiliary I/Os

- four LVDS configurable auxiliary inputs

- four LVDS configurable auxiliary outputs

- two separate LVDS pixel clock, hsync and vsync outputs

- four opto-isolated configurable auxiliary inputs

- serial communication ports that can be mapped as PC COM ports

- · internal video generator for diagnostics

### Dimensions and environmental information

- 18.75 L x 10.7 H x 1.73 W cm (7.38" x 4.2" x 0.68") from bottom edge of goldfinger to top edge of board and without bracket and retainer

- power consumption (typical): 1.2A @ 3.3V or 3.96W, 1.1A @ 5V or 5.5W, 0.02A @ 12V or 0.24W, or 9.7W total

- operating temperature: 0°C to 55° C (32° F to 131° F)

- ventilation requirements: 50 LFM (linear feet per minute) over board(s)

- relative humidity: up to 95% (non-condensing)

- FCC class B (XCL), class A (eCL)

- CE class B (XCL), class A (eCL)

- RoHS-compliant

#### Software drivers

- Matrox Imaging Library (MIL) drivers for 32/64-bit Microsoft® Windows® XP/Vista®/7

- MIL drivers for 32/64-bit Linux®

## **Ordering Information**

#### Hardware

| Part number    | Description                                                                                                                  |

|----------------|------------------------------------------------------------------------------------------------------------------------------|

| HEL 5M SFCL*   | PCI-X® single-Full Camera Link® frame<br>grabber with 512 MB DDR SDRAM and<br>cable adapter board.                           |

| HEL 5M SFCL E* | x4 PCIe <sup>™</sup> single-Full Camera Link <sup>®</sup> frame<br>grabber with 512 MB DDR SDRAM and<br>cable adapter board. |

| HEL 5M DBCL*   | PCI-X® dual-Base Camera Link® frame<br>grabber with 512 MB DDR SDRAM and<br>cable adapter board.                             |

| HEL 5M DBCL E* | x4 PCIe <sup>™</sup> dual-Base Camera Link <sup>®</sup> frame<br>grabber with 512 MB DDR SDRAM and<br>cable adapter board.   |

#### Software

Refer to MIL datasheet.

#### Cables

Camera Link® cables available from camera manufacturer, 3M Interconnect Solutions (www.3m.com), Intercon1 (www.nortechsys.com/intercon) or other third parties.

Cables for cable adapter boards available from third parties.

#### Notes:

- 1. Refer to Camera Link® specification for more information.

- 2. Billion operations per second.

- 3. Only one source buffer for MAC unit.

- 4. Accelerated functions include MbufBayer (bilinear interpolation)

MimArithMultiple(M\_OFFSET\_GAIN, M\_WEIGHTED\_AVERAGE,

M\_MULTIPLY\_ACCUMULATE], MimArith(M\_ADD, M\_ADD\_CONST, M\_SUB,

M\_SUB\_CONST, M\_SUB\_ABS, M\_MULT, M\_MULT\_CONST, M\_CONST\_SUB,

M\_AND, M\_NAND, M\_OR, M\_XOR, M\_NOR, M\_XNOR, M\_NOT, M\_AND\_CONST,

M\_NAND\_CONST, M\_OR\_CONST, M\_XOR\_CONST, M\_NOR\_CONST,

M\_XNOR\_CONST, M\_NEG, M\_ABS, M\_MIN, M\_MIN\_CONST, M\_MAX,

M\_MAX\_CONST], MimResize(with specific factors), MimDilate(I),

MimErode(I), MimThin(I), MimThick(I), MimDistance(I), MimConnectMap(I),

MimMorphic(M\_DILATE, M\_ERODE, M\_THICK, M\_THIN, M\_MATCH),

MimConvolve(M\_SMOOTH, M\_SHARPEN, M\_VERT\_EDGE, M\_HORIZ\_EDGE,

M\_LAPLACIAN\_EDGE, M\_EDGE\_DETECT], MimLutMap(8-bit), MimShift(I),

MimBinarize(I), MimClip(I), MimConvert(M\_YUV16\_TO\_RGB,

M\_RGB\_TO\_YUV16, M\_RGB\_TO\_L, M\_L\_TO\_RGB, M\_RGB\_TO\_Y), MimFlip(I),

MimFindExtreme(I), MimCountDifference(I) and ActiveMIL equivalents.